7 nm bis 3 nm: Bei TSMC geht es mit der Halbleiterfertigung zügig voran, was exklusiver Technik bei Masken und Packaging zu verdanken ist.

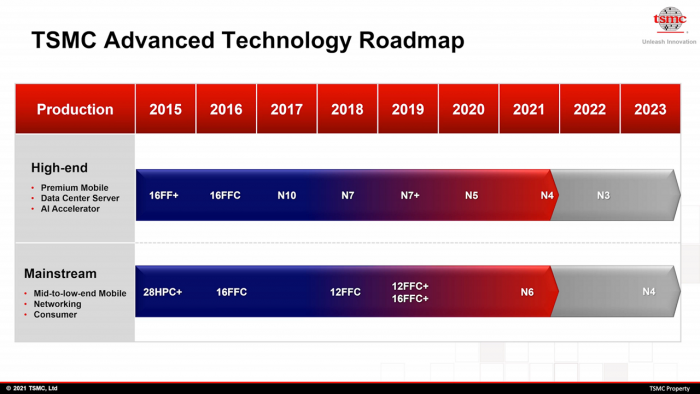

TSMC hat auf dem alljährlichen Technology Symposium einen Überblick gegeben, wie der Stand der Technik heute und in naher Zukunft ist: Der weltweit größte Auftragsfertiger setzt von 7 nm bis 3 nm samt Zwischenstufen auf allerhand Prozesse, um möglichst vielfältige Kundenwünsche abzudecken, und legt auch beim Packaging wortwörtlich einen oben drauf.

Aktueller Stand bei TSMC sind diverse 7-nm- sowie 6-nm- und 5-nm-Verfahren: Den N7 genannten Node mit klassischer Immersionslithografie (DUV) nutzt beispielsweise AMD für aktuelle Epyc- und Ryzen-CPUs sowie Radeon-GPUs; für spezielle Partner hat TSMC zudem N7HPC entworfen. Zwar gibt es mit N7+ auch eine Variante mit extrem ultravioletter Belichtung (EUV), diese wird aber kaum verwendet.

Stattdessen entschieden sich viele Partner direkt für N5 und dessen optimierten N5P-Ableger, unter anderem Apple beim A14- und beim M1-Chip. Laut TSMC hat N5 einen rasanten Start hingelegt, innerhalb von sechs Monaten seit Beginn der Serienfertigung liegt der Wafer-Output deutlich höher als bei N7 oder 16FF. Hinzu kommt, dass weniger Defekte anfallen als bei N7/N6, was die Ausbeute (Yield) steigert, und dass es mit N5HPC ebenfalls eine leistungsgesteigerte Variante gibt.

N6 für AMDs Ryzen 6000

Nicht minder erfolgreich ist N6: Das Verfahren ist weniger für Highend-Chips wie CPUs oder GPUs gedacht, sondern bedient Bereiche wie Midrange-Smartphone-SoC und in der extra entwickelten N6RF-Variante auch Mobilfunk/WiFi-Anwendungen. Diese wurden bisher oft mit 16FF+ oder 12FFC (eine Kompaktversion) produziert, weshalb der Sprung auf N6 gigantisch ausfällt. Auch für Chiplet-Designs bietet sich N6 an, so soll AMD den Node für das I/O-Die der Raphael-CPUs alias Ryzen 6000 nutzen und mit Zen-4-CPU-Dies auf N5-Basis koppeln.

Mit N4 gibt es bereits einen Nachfolger, die Risk Production soll im dritten Quartal 2021 beginnen. N4 fußt auf N5, laut TSMC handelt es sich um einen optischen Shrink rein für die Chiplogik statt auch für den SRAM, weshalb die Fläche um 6 Prozent reduziert werden soll. Die Yield-Rate sei schon ähnlich gut wie bei N5, aus diesem Grund dürfte sich N4 ebenso wie N6 künftig lange anhaltender Beliebtheit erfreuen.

N3 als Top-Node für 2022

Das nächste Highend-Verfahren heißt N3 und soll verglichen mit N5 eine bis zu 15 Prozent höhere Geschwindigkeit bei gleicher Leistungsaufnahme oder aber die gleiche Performance bei bis zu 30 Prozent weniger Energiebedarf aufweisen. Weil es sich um einen sogenannten Full-Node handelt, soll überdies die Logikdichte um 70 Prozent steigen, die für SRAM immerhin um 20 Prozent.

Laut TSMC wird N3 exzellent aufgenommen, so soll es im ersten Jahr mehr als doppelt so viele Node-Tape-Outs (NTO) geben wie bei N5. Die Serienproduktion ist für das zweite Halbjahr 2022 vorgesehen.

Weiter geht's mit selbst entworfenen Membranen und dem FinFet-Nachfolger.

Ein wichtiger Punkt bei Nodes wie N3 und N5 ist die Yield-Rate, da die extrem ultraviolette Belichtung (EUV) besondere Herausforderungen mit sich bringt. Zwar lässt sich bisher noch die äußerst aufwendige Mehrfachbetrahlung, etwa via Quad-Patterning, vermeiden - dafür sind die notwendigen Masken noch empfindlicher als bei DUV.

Um diese zu schützen und somit defekte Chips zu vermeiden, werden die Fotomasken mit einer speziellen Membran versehen, dem Pellikel. Zwar lässt sich EUV auch ohne nutzen, jedoch mit signifikant höherem Aufwand und steigender Fehlerrate. Weil TSMC laut eigener Aussage die Hälfte aller weltweit von ASML ausgelieferten EUV-Stepper installiert hat, war für die beste Ausbeute ein selbst entwickeltes Pellikel von höchster Bedeutung.

Und genau das hat TSMC geschafft: Während ASML die eigene Membran via Mitsui Chemicals gerade erst ausliefert, gibt TSMC an, mit steigender Pellikelverfügbarkeit die EUV-Maskenhaltbarkeit bis 2021 fast auf DUV-Niveau bringen zu wollen. Ob Intel oder Samsung Foundry für die EUV-Fertigung ebenfalls eine entsprechende Schutzfolie entworfen haben oder zumindest daran arbeiten, ist uns nicht bekannt.

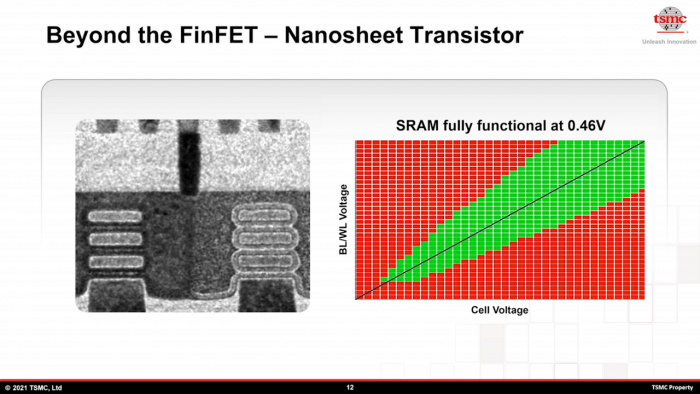

Gate All Around auch bei TSMC

Auch für die Generationen nach N3 hat TSMC schon Ideen: Statt an FinFets arbeitet der Auftragsfertiger an GAA-Fet (Gate All Around) auf Basis von Nanosheets, entsprechender SRAM wurde 2021 gezeigt und Samsung Foundry plant diese Technik beim 3GAE-Node einzusetzen. Auch Transistoren aus kristallinen 2D-Materialien und Kohlenstoffnanoröhren stehen bei TSMC auf dem Plan, diese werden als Alternative zu Silizium-basierten Chips erforscht.

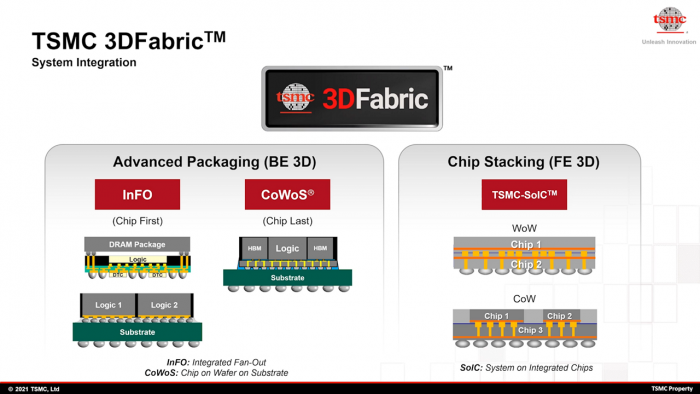

Neben der eigentlichen Halbleiterfertigung legt TSMC den Fokus immer stärker auf Packaging-Technik, um die steigende Nachfrage für Chiplet-Designs zu bedienen; zusammengefasst werden diese als 3D Fabric. Auch hier hat TSMC diverse Eigenentwicklungen parat, die wichtig für kommenden Chip-Designs sind. Zudem gilt es neue Werke für die Produktion ebendieser zu errichten.

So ist InFo (Integrated Fanout) als Packaging-Technik für PoP (Package on Package) im Smartphone-Segment weit verbreitet, um Mobile-SoCs mit LPDDR-Speicher zu verbinden. Neu ist InFO_B für bis zu 20 Prozent größere Chips, die auch dicker sein dürfen - was die thermischen Eigenschaften positiv beeinflusst.

CoWoS (Chip on Wafer on Substrat) wiederum kommt bei vielen ASICs und GPUs zum Einsatz, um HBM-Stapelspeicher auf einem Interposer zu verknüpfen. Bisher war das Limit für Letzteren die doppelte Maskenfläche (Reticle), noch 2021 will TSMC es auf das Dreifache erweitern, um HBM2E-Designs mit gleich acht statt sechs Stacks zu produzieren.

Eine neuere Entwicklung ist SoIC (System on Integrated Chips), das es in zwei Ausführungen gibt: Bei WoW (Wafer-on-Wafer) werden gleich große Chips verwoben, bei CoS (Chip-on-Wafer) hingegen ein Basis- und ein Deckel-Die mit unterschiedlichen Maßen. Ein aktuelles Beispiel dafür ist AMDs kürzlich vorgestellter 3D V-Cache für Ryzen-CPUs, der CoS nutzt.

Chip-on-Wafer für Ryzen mit 3D V-Cache

Die Produktion soll Ende 2021 starten, was zu TSMCs Angabe passt, dass N7-auf-N7-CoS in diesem Zeitraum bereit stehen soll. N5 auf N5 ist für 2022 geplant - hallo Zen 4! - und N3 (oben) auf N5 (unten) ist bisher für 2023 angesetzt.

Um genügend Kapazitäten bereitstellen zu können, baut TSMC fleißig Fabs (Semiconductor Fabrication Plants) und APs (Advanced Packing & Testing): Im taiwanischen Tainan ist die Fab 18 halb fertig, drei Lines/Phasen laufen mit 5 nm und eine vierte befindet sich in der Konstruktion; drei weitere für 3 nm sind in Arbeit.

In Hsinchu soll künftig die Fab 20 für 2 nm stehen und im US-Bundesstaat Arizona wird mit der Fab 21 für 5 nm das erste US-Werk entworfen. TSMC hat ergo in den nächsten Monaten richtig viel vor.

Halbleiterfertigung: Was TSMC in den nächsten Monaten vorhat - Golem.de - Golem.de

Read More

No comments:

Post a Comment